Philips Semiconductors

#### Abstract

This report gives a description of the TDA933X-N1 version, together with application aspects.

Purchase of Philips  $I^2C$  components conveys a license under the  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

© Philips Electronics N.V. 1998

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

# **APPLICATION NOTE**

# Application information for I2Cbus controlled TV-processor TDA933XH

# AN98073

Author(s): P.C.T.J. Laro R.P. Vermeulen

Design & Application Department, Consumer ICs Nijmegen, The Netherlands

#### Keywords

Synchronisation H/V Single / Double scan, VGA Geometry on vertical and E-W Continuous cathod calibration I<sup>2</sup>C controlled

Date: October 1998

#### Summary

This report gives a description of the TDA933X together with application aspects. The TDA933X is the combination of a RGB output processor an a deflection processor, suitable for single scan, double scan and VGA.

# Philips Semiconductors TDA9330/31/32 H TV Display processor

# Application Note AN98073

#### CONTENTS

| 1. INTRODUCTION                                                                                                                                                   | 9        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2. DEVICE INFORMATION                                                                                                                                             | 13       |

| 2.2 Device description per functional block<br>2.2.1 Horizontal synchronisation<br>2.2.2 Vertical synchronisation/deflection and geometry (horizontal & vertical) | 16<br>22 |

| 2.2.3 RGB processing and control<br>2.2.4 I <sup>2</sup> C bus description                                                                                        |          |

| 3. APPLICATION INFORMATION                                                                                                                                        |          |

| 3.1 General                                                                                                                                                       |          |

| 3.2 Application remarks per functional block and per pin                                                                                                          |          |

| 3.2.1 Horizontal synchronisation                                                                                                                                  |          |

| 3.2.2 Geometry (drive of vertical deflection) and Vertical & Horizontal                                                                                           |          |

| 3.2.3 RGB processing and control.                                                                                                                                 |          |

| 3.2.4 Supply, decoupling and grounding                                                                                                                            |          |

| 3.3 Application of non-used pins                                                                                                                                  | 85       |

| 4. ALIGNMENTS                                                                                                                                                     | 87       |

| 4.1 Colour temperature alignment                                                                                                                                  |          |

| 4.2 Geometry alignment                                                                                                                                            |          |

| 5. REMARKS FOR THE TDA 933X N1 VERSION                                                                                                                            |          |

| 6. REFERENCES                                                                                                                                                     | 91       |

# LIST OF FIGURES

| 13 |

|----|

| 18 |

| 20 |

| 23 |

| 25 |

| 26 |

| 33 |

| 34 |

| 37 |

| 38 |

| 39 |

| 40 |

| 62 |

| 63 |

| 64 |

| 65 |

| 66 |

| 67 |

| 69 |

| 70 |

| 73 |

| 75 |

| 76 |

| 77 |

| 77 |

| 78 |

| 78 |

| 79 |

| 81 |

| 81 |

|    |

# SYSTEM DIAGRAMS

| A 1: BLOCK DIAGRAM: HORIZONTAL AND VERTICAL SYNCHRONISATION | 21  |

|-------------------------------------------------------------|-----|

| A 2: BLOCK DIAGRAM: GEOMETRY ON VERTICAL AND E-W DRIVE      | 31  |

| A 3: BLOCK DIAGRAM: YUV/RGB PROCESSING.                     | 35  |

| A 4: BLOCK DIAGRAM: RGB-PROCESSING AND CONTROL.             | 43  |

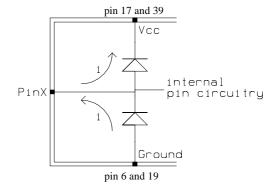

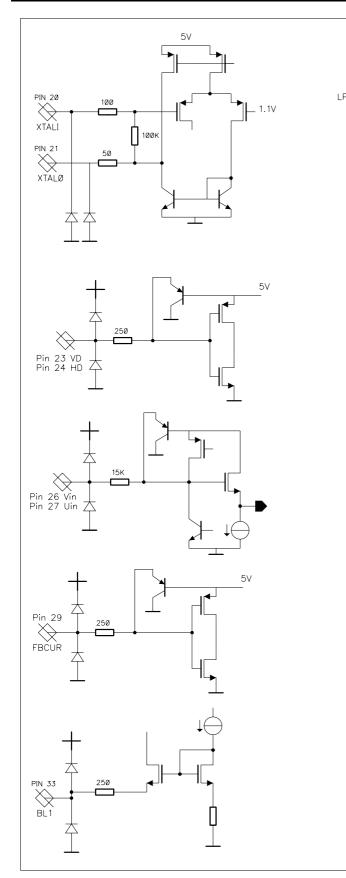

| B 1 : INTERNAL PINNING DIAGRAM (1-11)                       | 93  |

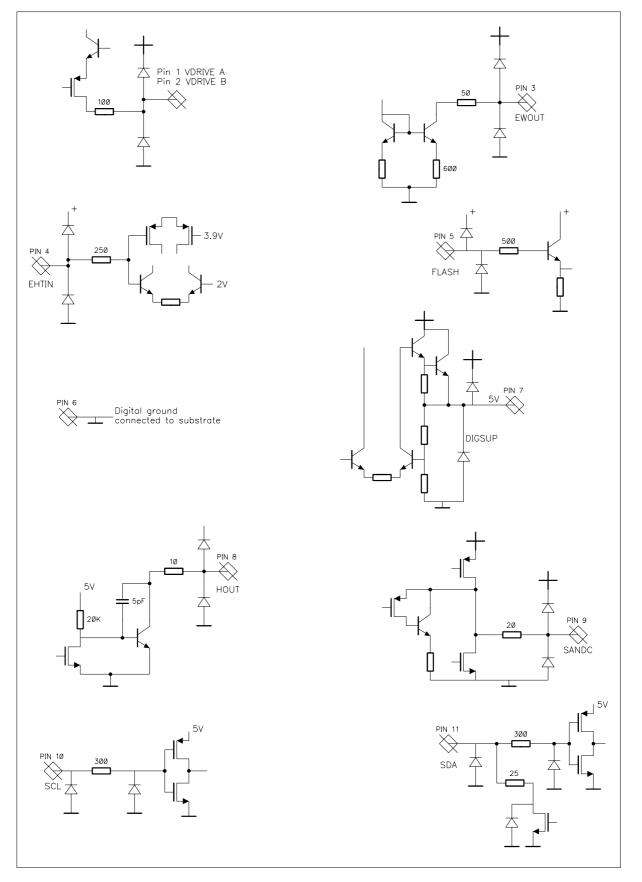

| B 2 : INTERNAL PINNING DIAGRAM (12-19)                      | 95  |

| B 3 : INTERNAL PINNING DIAGRAM (20-34)                      | 97  |

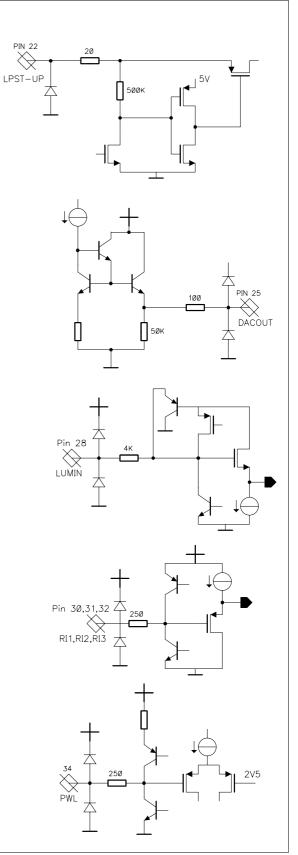

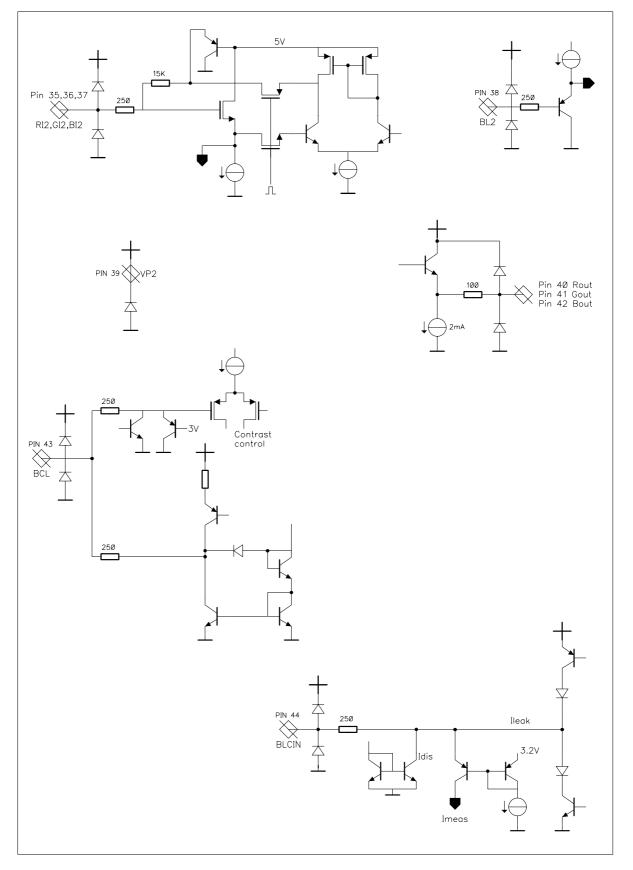

| B 4 : INTERNAL PINNING DIAGRAM (35-44)                      | 99  |

| C 1 : APPLICATION DIAGRAM OF TDA933X                        | 101 |

# LIST OF TABLES

| TABLE 1 : SURVEY FEATURES / TYPE                          | 12 |

|-----------------------------------------------------------|----|

| TABLE 2 : APPLICATION INFO PER PIN NUMBER                 | 14 |

| TABLE 3 : APPLICATION INFO PER PIN NAME                   | 15 |

| TABLE 4 : CONDITION PHI-1 LOOP                            | 44 |

| TABLE 5 : H/V SETTINGS FOR ASPECT RATIO'S AS 16:9 AND 4:3 | 73 |

TV Display processor

#### 1. INTRODUCTION

This report gives a description of the TDA933X together with application aspects. The TDA933X is the successor of the TDA 478X RGB processor and TDA 9150 deflection processor. It has a higher degree of integration and additional features.

The TDA933X is a combination of a RGB output processor and deflection processor with  $I^2C$  control. The TDA933X matches ideal with the versatile TDA9321 (see ref. 2, 4) input processor (IF + video switches + full multistandard colour decoder) for set architectures using extra YUV processing like PAL plus and scan conversion (progressive scan or "100 Hz").

All chips contain the RGB control processing with YUV input, 2 linear RGB inputs one of which has a blending option, deflection processing with H and V input, stable clock generation using an external X-tal/resonator, drive signal generation for horizontal & vertical deflection and East West (diode modulator).

Versions are available with VGA option, having a multi-sync mode for horizontal synchronisation between 30 - 50 kHz (or 15 - 25 kHz) and stabilised vertical amplitude independent of the vertical frequency.

The number of external components required for application is considerably less than equivalent two or three chip concepts. All necessary alignments can be done via I<sup>2</sup>C control.

The device is available in QFP 44 (Quad Flat Pack, 44 pins) package.

The complete integration of all functions on a single chip has been realised using the BIMOS technology (combined BIpolar and MOS). The high frequent bipolar process is used for video processing. The MOS process is used for all digital parts. Due to MOS components, it is possible to integrate very large time constants.

TV Display processor

#### 2. DEVICE INFORMATION

The TDA933X TV display processor is the combination of a RGB output processor and deflection processor

The device matches ideal with the versatile input processor TDA9321 (see ref. 2, 4, IF + video switches + full multi-system colour decoder including Pal plus helper demodulation) in set architectures with additional YUV processing like PAL plus or scan conversion (progressive scan or "100 Hz").

Below the features available in all versions will be discussed. The additional features are described separately.

#### Available in all versions

#### RGB

- RGB control (brightness, contrast, saturation)

- Improved black current stabilisation (continuous cathode calibration)

- White point adjustment

- Blue stretch which offsets colours near white to blue

- Option to insert "blue back" when no video signal is available

- Black stretching of non standard luminance signals

- Switchable matrices for colour difference signals

#### Input

- YUV input

- Linear RGB input 1 with fast blanking for SCART RGB or VGA signals with full control (brightness, contrast, saturation)

- Linear RGB input 2 for TEXT / OSD with blending option for mixing YUV or RGB 1 input with TEXT / OSD. RGB input 2 has only brightness control

#### Synchronisation and Deflection

- Stable clock generation using an external 12 MHz ceramic resonator or X-tal

- Suitable for single scan (1 Fh, 1 Fv), progressive scan (2 Fh, 1 Fv) and double scan (2 Fh, 2 Fv) applications

- Horizontal synchronisation with two control loops and alignment free horizontal oscillator

- Slow start and slow stop of the horizontal drive output to enable low stress start-up and switch-off from the line circuit at nominal line supply voltage.

- Low power start-up option to generate horizontal drive pulses from only 5V/3mA supply

- Vertical count-down circuit for stable behaviour, including absence of  $H_D / V_D$  synchronisation pulses

- Horizontal and vertical geometry control

- Vertical drive optimised for DC coupled vertical output stages

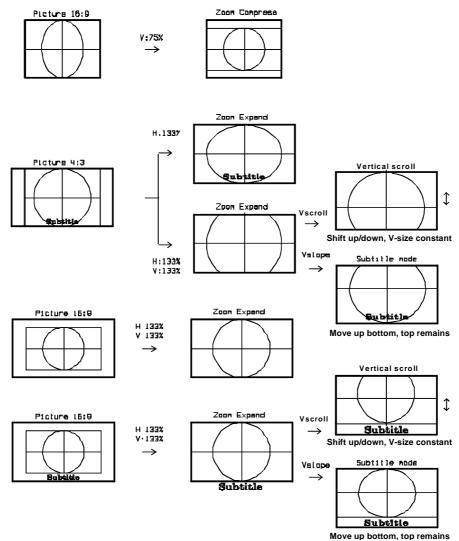

- Independent horizontal and vertical linear zoom for 16:9 expand or 4:3 compress

- Horizontal range: 65% to 100%

- Vertical range: 75% to 138%

- Vertical blanking for overscan

- Extended horizontal blanking to display a 4:3 picture on a 16:9 tube while blanking the standard 6% overscan which is not visible on a 4:3 tube.

- Vertical scroll for optimal display in combination with vertical zoom

- Option to switch-off in the vertical overscan to minimise visability of the discharge of the picture tube..

#### Control

- Full I2C bus control, as well for customer controls as for factory alignment

#### **Power consumption**

Low power consumption

#### Packaging

- QFP-44 (Quad Flat Pack, 44 pins SOT 307-2)

#### **Additional features**

The additional features, varying per type, are described below. In table 1 the featuring per type is given.

#### Synchronisation and Deflection

- VGA multi-sync mode with a horizontal frequency range of 30 50 kHz (2 Fh mode) or 15 25 kHz (1 Fh mode) and stabilised vertical amplitude independent of the vertical frequency

- Linear DC output proportional to the horizontal frequency for power supply adaptation

#### Survey of additional features / type

| IC version                                                | TDA9330H | TDA9331H | TDA9332H |

|-----------------------------------------------------------|----------|----------|----------|

| VGA mode                                                  |          | Х        | Х        |

| DAC output voltage (pin 25) I <sup>2</sup> C controlled   | Х        |          | Х        |

| DAC output voltage (pin 25) proportional to VGA frequency |          | Х        |          |

Table 1 : Survey features / type

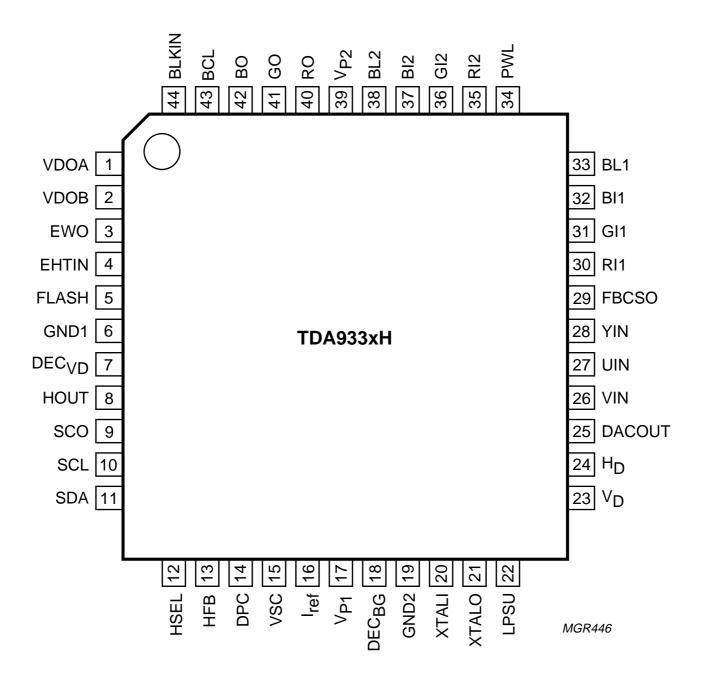

#### 2.1 Pinning configuration for QFP-44

The TDA933X is available in Quad Flat Package QFP-44 SOT 307-2.

Fig 1 : Pinning diagram of QFP44

#### 2.2 Device description per functional block

The TDA933X is organised in functional blocks. These different blocks are:

Horizontal and vertical synchronisation Horizontal and vertical geometry RGB processing & control Supply decoupling Control I<sup>2</sup>C bus

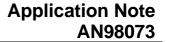

A description of each functional block has been made together with the corresponding block diagrams. The internal circuits, connected to the pins, are shown on page 93 to 99.

| In the table below, all pin numbers are | given with the page number | where application information can be found. |

|-----------------------------------------|----------------------------|---------------------------------------------|

|-----------------------------------------|----------------------------|---------------------------------------------|

| Pin | Page | Pin | Page | Pin | Page | Pin | Page |

|-----|------|-----|------|-----|------|-----|------|

| 1   | 69   | 12  | 63   | 23  | 71   | 34  | 76   |

| 2   | 69   | 13  | 63   | 24  | 67   | 35  | 74   |

| 3   | 70   | 14  | 64   | 25  | 68   | 36  | 74   |

| 4   | 71   | 15  | 71   | 26  | 74   | 37  | 74   |

| 5   | 61   | 16  | 71   | 27  | 74   | 38  | 75   |

| 6   | 82   | 17  | 82   | 28  | 74   | 39  | 82   |

| 7   | 82   | 18  | 82   | 29  | 81   | 40  | 76   |

| 8   | 61   | 19  | 82   | 30  | 74   | 41  | 76   |

| 9   | 62   | 20  | 66   | 31  | 74   | 42  | 76   |

| 10  | -    | 21  | 66   | 32  | 74   | 43  | 76   |

| 11  | -    | 22  | 67   | 33  | 74   | 44  | 78   |

Table 2 : Application info per pin number

| PIN NAME | PIN # | <b>PIN DESCRIPTION</b>                 | PAGE # |

|----------|-------|----------------------------------------|--------|

| BCL      | 43    | Beam current limiting input            | 76     |

| BI1      | 32    | Blue input 1                           | 74     |

| BI2      | 37    | Blue input 2                           | 74     |

| BL1      | 33    | RGB 1 insertion switch input           | 74     |

| BL2      | 38    | RGB 2 insertion switch input           | 75     |

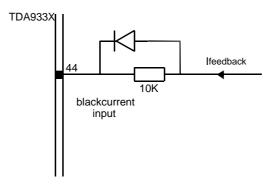

| BLCIN    | 44    | Black current input                    | 78     |

| BO       | 42    | Blue out                               | 76     |

| DACOUT   | 25    | DAC output                             | 68     |

| DECBG    | 18    | Bandgap Decoupling                     | 82     |

| DIGSUP   | 7     | Digital supply decoupling              | 82     |

| DPC      | 14    | PHI-2 dynamic phase compensation input | 64     |

| EHTIN    | 4     | EHT tracking / overvoltage protection  | 71     |

| EWOUT    | 3     | EW drive                               | 70     |

| FBCSO    | 29    | Fixed beam current switch-off input    | 81     |

| FLASH    | 5     | Flash detection input                  | 61     |

| GI1      | 31    | Green input 1                          | 74     |

| GI2      | 36    | Green input 2                          | 74     |

| GND1     | 6     | Grounding                              | 82     |

| GND2     | 19    | Grounding                              | 82     |

| GO       | 41    | Green output                           | 76     |

| HD       | 24    | Horizontal synchronisation input       | 67     |

| HFB      | 13    | Flyback input                          | 63     |

| HOUT     | 8     | Horizontal drive                       | 61     |

| HSEL     | 12    | Horizontal frequency selection         | 63     |

| IREF     | 16    | Reference current                      | 71     |

| LPSU     | 22    | Low power start-up                     | 67     |

| NDOA     | 1     | Vertical drive                         | 69     |

| NDOB     | 2     | Vertical drive                         | 69     |

| PWL      | 34    | Peak white limiting capacitor          | 76     |

| RI1      | 30    | Red input 1                            | 74     |

| RI2      | 35    | Red input 2                            | 74     |

| RO       | 40    | RGB output                             | 76     |

| SANDC    | 9     | Sandcastle output/Vertical guard input | 62     |

| SCL      | 10    | I2C Clock line                         | -      |

| SDA      | 11    | I2C Data line                          | -      |

| UIN      | 27    | U input                                | 74     |

| VD       | 23    | Vertical synchronisation input         | 71     |

| VIN      | 26    | V input                                | 74     |

| VP1      | 17    | Supply                                 | 82     |

| VP2      | 39    | Supply                                 | 82     |

| VSC      | 15    | Vertical sawtooth                      | 71     |

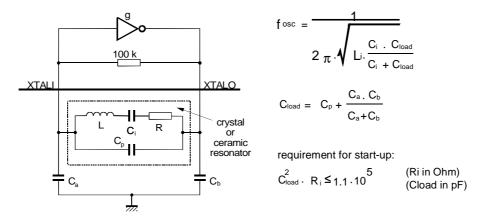

| XTALI    | 20    | Reference oscillator input             | 66     |

| XTALO    | 21    | Reference oscillator input             | 66     |

| YIN      | 28    | Y input                                | 74     |

Table 3 : Application info per pin name

#### 2.2.1 Horizontal synchronisation

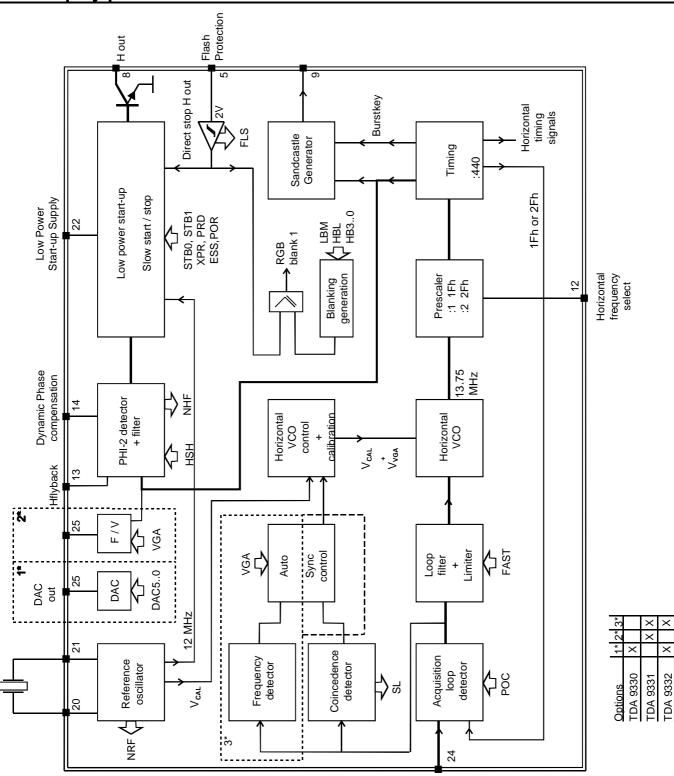

See also the related block diagram (A 1 on page 21).

The main functions are:

- \* Horizontal oscillator, reference oscillator and acquisition loop ("PHI-1")

- \* PHI-2 detector and sandcastle generation

- \* Horizontal output with slow start/stop facility

- \* Flash protection

#### \* Main function description

Next, the main functions for sync will be described. See also the related paragraphs in the chapter I<sup>2</sup>C bus description.

#### \* Horizontal oscillator, reference oscillator and acquisition loop ("PHI-1")

The horizontal oscillator requires no external components and is fully integrated. The oscillator consists of a VCO, running at a frequency of 880 \* Fh = 880 \* 15.625 kHz = 13.75 MHz.

The horizontal VCO is controlled by:

- The loop filter voltage

- The calibration voltage  $V_{CAL}$  from the reference oscillator (for free running mode)

- The voltage from the auto synchronisation loop (only for types with VGA mode)

The calibration voltage  $V_{CAL}$  which stabilises the free running frequency is generated by the 12 MHz reference oscillator block which needs an external resonator. It is also possible to use a 12 MHz X-tal as reference or to feed an external 12 MHz reference signal to pin 20.

The correct calibration of the horizontal VCO by the reference oscillator can be checked reading bit **NRF**. This bit should be checked under the following conditions, because when the horizontal VCO is not locked to the reference oscillator, the frequency of the horizontal drive can be incorrect:

- At power-on / initialisation before switching-on the horizontal drive

- After power dip (shutdown detection, **POR** = 1), re-initialisation is required

The horizontal frequency for H-drive and reference signal for the acquisition loop ("PHI-1") and PHI-2 is derived from the horizontal VCO frequency using a divider chain. In this chain, various timing signals are derived for signal processing in all blocks.

An acquisition loop, consisting of a PLL with built-in loop filter, locks the horizontal VCO to the incoming synchronisation signal  $H_D$  using a phase detector with as input  $H_D$  and the divided VCO signal. The signal  $H_D$  is generated by the input processor (e.g TDA9321) or by scan conversion circuitry.

The loop filter is integrated. The loop speed can be increased by 30 % by decreasing the internal time constant by 30% setting  $I^2C$  bit **FAST** to 1,

Though this function is analogue to the PHI-1 loop of synchronisation circuits, this phase detector loop has only the task to synchronise the horizontal VCO with the  $H_D$  input and lacks therefore the sync separator, gating functions and different loopfilter time constants for synchronising under bad and noisy signal conditions.

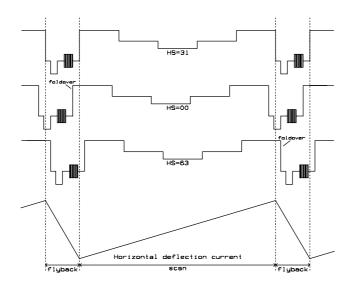

#### Selection between 1 Fh and 2 Fh mode

The horizontal frequency can be set to 1 Fh or 2 Fh using a switchable divide-by-2 or divide-by-1 prescaler. The selection of the prescaler is hard wired for robustness. By connecting pin 12 to ground the prescaler is set to divide-by-2, giving 1 Fh horizontal frequency. By leaving pin 12 open, the prescaler is set to divide-by-1, giving 2 Fh horizontal frequency. Though this selection is meant for hard-wiring, it is possible to switch between 1 Fh and 2 Fh mode by pulling pin 12 low or not using a transistor. Because the status of pin 12 is only checked when switching on from stand-by, changing the level on pin 12 will first take effect when both stand-by bits **STB1,0** are toggled from 0 0 to 1 1. In this way, switching the level on pin 12 while the horizontal output is running will not change the horizontal output frequency, preventing damage to the horizontal deflection stage. However, for safe behaviour under various conditions (e.g. power supply dips) we advice to **switch only pin 12 while the TDA933X is in stand-by mode.**

**Philips Semiconductors**

### TDA9330/31/32 H TV Display processor

#### TV-mode

When no  $H_D$  pulse is present, the free running horizontal frequency is set to 16.05 kHz (1 Fh mode) or 32.1 kHz (2 Fh mode)

In TV-mode, the horizontal oscillator range is limited to - 5 % to + 10 % to prevent damage to the deflection stage. Also the maximum correction speed of the acquisition loop is limited to 2  $\mu$ s per line in 1 Fh mode and 1  $\mu$ s per line in 2 Fh mode.

#### VGA mode

For VGA mode, the horizontal oscillator can lock to incoming frequencies from 15 - 25 kHz in 1 Fh mode and from 30 - 50 kHz in 2 Fh mode.

When not locked to an incoming  $H_D$  pulse, the horizontal oscillator will run at its lowest frequency. When a  $H_D$  pulse is offered, a frequency difference detector will adjust the centre frequency of the horizontal VCO with a maximum speed of 100 kHz/s to the incoming frequency, after which the phase detector of the acquisition loop takes over and keeps the VCO synchronised.

Both horizontal and vertical synchronisation pulses have to be positive, so if synchronisation to different VGA standards with positive and negative sync pulses is needed, these sync signals have to be converted to positive polarity before feeding to the  $H_D$  input pin 24 and  $V_D$  input pin 23.

#### Coincidence detector, Synchronisation Lock bit SL

The coincidence detector detects whether the horizontal oscillator is synchronised with the incoming  $H_D$  pulse, thus whether the acquisition loop is in-lock. The output is available by I<sup>2</sup>C bus, **SL**, and can be used to check whether the loop is working correct.

Note that when the acquisition loop is disabled (see below, **POC**=1) **SL** is always 0.

#### Free running mode

By setting **POC** to 1, the acquisition loop is disabled and the horizontal oscillator will run at its free run frequency. The frequency is pending on the chosen mode (1 Fh or 2 Fh, see above). This frequency is stable because it is derived from the 12 MHz reference oscillator and is not disturbed by spurious signals on the  $H_D$  input.

This mode can be used for installation menus and also for stable blue mute when no valid signal is present. Because **SL** of the TDA 933X cannot be used to detect a valid input signal on the  $H_D$  input, an external coincidence detector (e.g. **IFI** or **SL** from the TDA 9321 input processor) should be used to detect the presence of a valid signal.

#### \* PHI-2 detector and sandcastle

As described, the acquisition PLL ("PHI-1 loop") synchronises the horizontal oscillator with the incoming  $H_D$  pulses. The PHI-2 loop synchronises the deflection drive to obtain a stable horizontal position of the picture on the screen.

This is necessary because due to beam current variations, the storage time of the line transistor varies. These storage time variations have to be compensated by adapting the phase of the horizontal drive, pin 8, to prevent horizontal shift of the picture on screen.

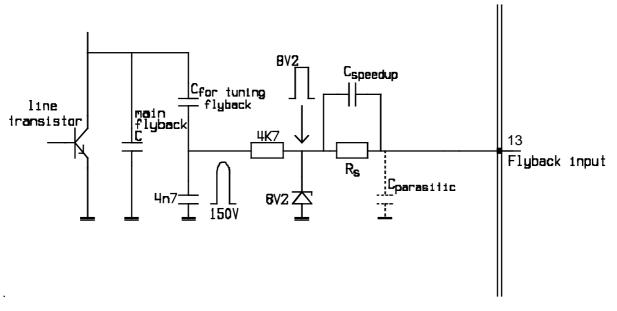

The horizontal flyback pulse is used as reference for the horizontal screen position. The PHI-2 detector compares the horizontal flyback input pulse, pin 13, with the horizontal oscillator signal and keeps the phase relation fixed. This fixes the horizontal position on the screen.

Using **HSH** (Horizontal **SH**ift), a fixed phase offset can be programmed for PHI-2. In this way the horizontal position of the picture can be centred on the screen.

Using **HP** (Horizontal **P**arallelogram), a phase offset change per line can be set. In this way, the phase offset changes from top to bottom of the screen. With this adjustment it is possible to set the vertical lines orthogonal to the horizontal lines (parallelogram correction) when the horizontal and vertical deflection yokes are not orthogonal.

The time constant of the PHI-2 loop is integrated. The correction factor K is 0.5. The correction factor is defined as the amount of correction of a phase error between flyback pulse and horizontal oscillator. With K = 0.5, the phase error is halved each line period.

For horizontal geometry correction related to varying EHT voltage, a dynamic phase correction input (pin 14) is provided. This input can be driven by the standard used circuits to measure the EHT voltage decrease for the beam current limiting function. The EHT info voltage should drop when the EHT drops. The level for no correction is 4.0 Volts.

#### Flyback input

The horizontal flyback input (pin 13) has two functions. The flyback pulse on this pin is used as input signal for the PHI-2 loop but also determines the horizontal blanking. For optimal performance, the voltage level at which the blanking starts is chosen low (0.3 Volt, maximum blanking time due to wider base of the flyback pulse) while for loop stability the slicing level for the PHI-2 reference is chosen higher (4.0 Volts).

The presence of a horizontal flyback pulse can be monitored by reading bit **NHF** (No Horizontal Flyback pulse). In this way, the  $\mu$ processor can monitor the correct working of the horizontal deflection stage.

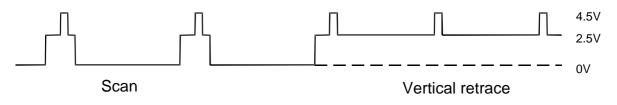

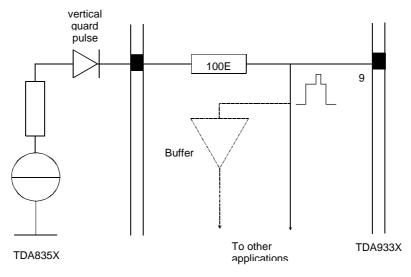

#### Sandcastle output/vertical guard input

The sandcastle output pin 9 is combined with the vertical guard input. The sandcastle signal timing is related to the  $H_D$  and  $V_D$  input signals and the flyback pulse.

Each horizontal line, a clamp pulse is generated. The delay from rising edge of the  $H_D$  to the clamp pulse start is 5.4 µs for 1 Fh and 2.7 µs for 2 Fh. The level is 4.5 volt typical. The clamp pulse width is 3.5 µs for 1 Fh and 1.8 µs for 2 Fh. The clamp pulse timing and generation is comparable to the burstkey pulse of the PHI-1 loop of the input processor. The clamp pulse has the same timing as the internal used clamp pulse for the YUV and RGB inputs.

When the flyback pulse on the flyback input pin rises above 0.3 Volt and starts the horizontal blanking, the level on the sandcastle pin rises to 2.5 volt.

During vertical retrace, the output voltage is kept at 2.5 Volts for 12 - 25 lines, pending on the horizontal and vertical frequency mode.

During scan, the output voltage is low.

The sandcastle pulse can be used as clamp and blanking reference for display generating devices like TXT decoders and PIP processors.

Fig 2 : Sandcastle waveform.

To prevent picture tube damage when the vertical deflection fails, a vertical guard function is added to this pin. During the vertical blanking, a current from 1 to 3 mA should be inserted to the pin during at least one line period. If such a pulse is not detected, failure of the vertical deflection circuit is assumed and the RGB outputs are blanked.

The vertical deflection family TDA8350 - TDA8358 has a special guard output pin for this function.

The vertical guard status can be read out via the bit **NDF** (No vertical **DeF**lection). The automatic blanking of RGB during vertical guard failure can be disabled by setting bit **EVG** (Enable Vertical Guard) to 0. **EVG** also has to be set to 0 when the vertical guard function is not used to prevent unwanted blanking of the RGB outputs.

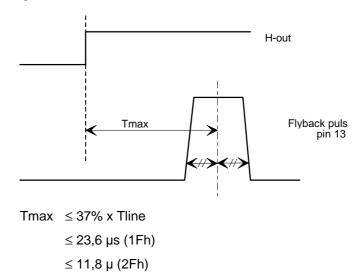

#### \* H-output and slow start/stop

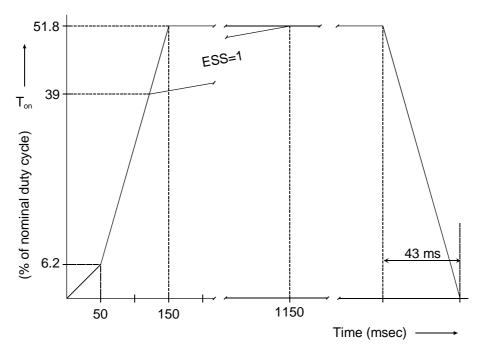

The horizontal output is the driver pin for the line deflection. It is an open collector output. Under normal operating condition the duty cycle of the output pulse is 48.2 % off (Hout=high) / 51.8 % on (Hout=low). Note that all percentages used in this chapter are related to the final cycle time of the horizontal output which can be 1 Fh, 2 Fh or varying from 15 to 50 kHz in VGA mode pending on the chosen mode.

When a horizontal flyback pulse is present at pin 13, Hout is always set high (Hout = off) irrespective the status of the output. In this way, switch-on of the line transistor during flyback time is prevented. The detection level is 0.3 Volt, so care must be taken to ensure that the level on this pin during scan is below 0.3 Volt under normal operating conditions.

Several provisions have been built-in to ease design and improve robustness of the deflection stage during switch-on and switch-off.

A build in slow start/stop circuit ensures a smooth start/stop behaviour of the line deflection and protects the line output transistor.

#### Switching on from stand-by via the stand-by bits STB1,0

During switch-on the horizontal output starts with a fixed off time (Hout=high) of 48.2 % while the on time (Hout=low) increases from 0% to 51.8 %. The on time increase from 0 % to 6.2 % lasts 50 ms, while the on time increase from 6.2 % to 51.8 % lasts 100 ms. These values lead in practice to a linear build-up of the EHT voltage in 150 ms while the horizontal frequency decreases from about double the final frequency to the final frequency.

Some picture tubes e.g. versions with DAF gun, are sensitive for flash-over when the EHT voltage rises too fast from 75% to 100% of the nominal EHT value. For these picture tubes, the EHT increase from 75% to 100% can be slowed down by setting bit **ESS** (Extended Soft Start) to 1. The on-time increase from 39% to 51.2% is then extended to 1000 ms. (See Fig 3).

#### Low power start-up

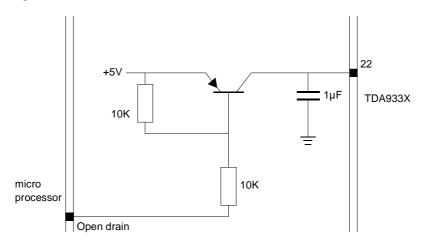

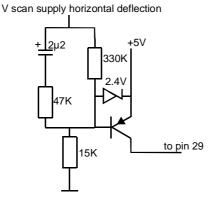

To ease the design of the stand-by power supply, a special low power start-up facility is built-in. This low power start-up mode can be activated by supplying 5 Volts to pin 22 when no 8 Volt is present on supply pins 17 and 39.

When 5 Volts is supplied, the horizontal output will start via a slow start procedure. The off time is fixed to 48.2 % and the on time is increased from 0 % to 12.5 % and remains running on this frequency. This horizontal drive should provide enough load for the power supply to wake it from stand-by mode and to build-up an 8 Volt supply using scan rectification of an auxiliary winding of the FBT for supplying pin 17 and 39 of the TDA 933X.

When the 8 Volt supply is present and the **POR** has been cleared by reading the status bytes and successful calibration of the horizontal VCO is confirmed by checking **NRF** = 0, all I<sup>2</sup>C registers must be written including **STB1,0** = 1 1. Then the on time of Hout is increased further from 12.5 % to 51.8 % according the slow start procedure as described above. When the H-out is not switched on from stand-by within 2 fields after **POR** is cleared, the on time is reduced from 12.5 % to 0% to switch-off safe the deflection when the 8 Volt is malfunctioning.

When the 8 Volt is present and **STB1,0** is set to 1 1, the 5 volt supply on pin 22 should be removed to ensure that H-out can be switched off completely. As long as the +5 Volt is present, H-out will remain running at 12.5 % on/ 48.2 % off when set to stand-by or when the +8 Volt is removed.

This low power pin 22 only needs 3 mA supply current typical. In this way, the stand-by power supply design can be simplified because one voltage can be used for µprocessor and low power start-up while the power needed for the TDA 933X is only 15 mW (23 mW max.) compared to 400 mW (510 mW max.) and an 8 Volt supply when the TDA 933X is started up in normal mode.

#### Switching off to stand-by using STB1,0

When switching-off via the stand by bits (**STB1,0**) the off time remains fixed on 48.2 % while the on time decreases from 51.2 % to 0 % in 43 ms. The on time decrease starts first after the vertical scan and vertical flyback is completed. During the first 37 ms of the switch-off time, the RGB outputs can be driven to obtain a fixed beam current for discharging the picture tube when bit **FBC** (Fixed Beam Current switch-off) is set to 1. The monitoring of the beam current is done via the Continuous Cathode Calibration loop which stabilises the cut-off and drive for the picture tube. (see chapter RGB processing and control for details).

The visability of the picture tube discharge can be minimised by setting bit **OSO** (Overscan Switch Off) to 1. When switching to stand-by, after completion of the vertical scan and vertical flyback, the vertical deflection is kept fixed in overscan so the discharge takes place in the overscan.

#### Switching off using mains switch

Also provisions are available when the set is switched-off via the mains switch. An external circuit should monitor the supply voltage of the deflection. When this voltage decreases, pin 29 (Fixed Beam Current Switch Off) should be pulled high. From that moment, first the vertical scan and vertical flyback is completed.

When **FBC** is set to 1, the RGB outputs are then driven to obtain a fixed beam current for discharge of the picture tube. When **OSO** is set to 1, the vertical deflection is kept fixed in overscan to minimise visability of the discharge.

| Philips Semiconductors |                  |

|------------------------|------------------|

| TDA9330/31/32 H        | Application Note |

| TV Display processor   | AN98073          |

H-out will keep running on nominal frequency, but because the deflection supply voltage decreases, the EHT will decrease proportionally. H-out will continue running till the supply voltage of the TDA 933X drops below the **POR** (**P**ower **O**n **R**eset) level. Both H-out and RGB drive will then be stopped.

See also chapter RGB control, paragraph Fixed beam current discharge.

Fig 3 : Slow start / slow stop horizontal output.

#### \* Flash protection

To protect the horizontal deflection stage during flash-over, the flash input pin 5 can be used. By pulling this pin above 2 Volts, the Hout is disabled immediately. When the voltage drops below 1.8 Volts, the horizontal output is started up again via the slow start procedure. This protection is hard wired and does not need intervention of the  $\mu$ processor. The status of the flash input can be read via status bit **FLS**, so the  $\mu$ processor can take additional action when needed.

An external flash detection circuit has to be applied to use this function. The hysteresis of the input prevents unstable behaviour.

For another protection facility, see paragraph "EHT compensation and overvoltage protection" in chapter "Vertical synchronisation/deflection and geometry (horizontal and vertical)".

Philips Semiconductors TDA9330/31/32 H

**TV Display processor**

Application Note AN98073

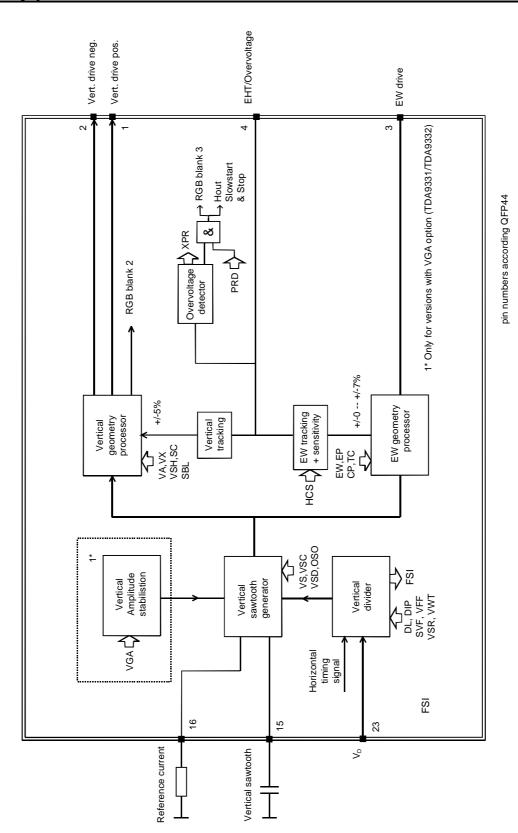

A 1: Block diagram: Horizontal and vertical synchronisation

무

#### 2.2.2 Vertical synchronisation/deflection and geometry (horizontal & vertical)

See also the related block diagram as well as the diagrams at the end of the report.

We can distinguish the following main blocks, which will be described in more detail below:

- \* Vertical divider system

- \* Vertical sawtooth generator

- \* Vertical geometry processor

- \* Horizontal (E-W) geometry processor

- \* EHT tracking + overvoltage protection

#### \* Vertical divider system

The divider system uses a counter that delivers the timing for the vertical ramp generator in the geometry processor. The clock is derived from the horizontal line oscillator.

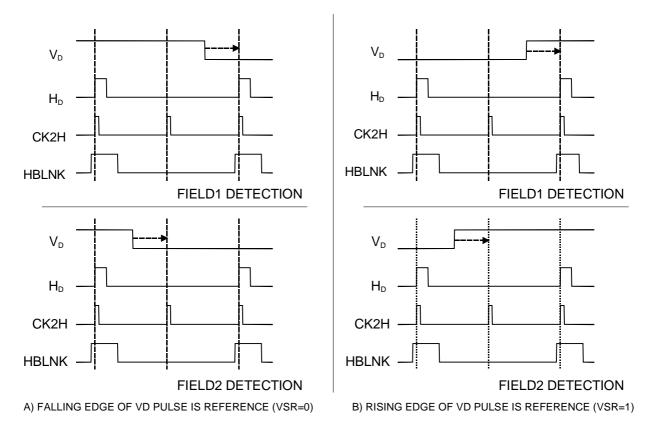

The divider system synchronises on the  $V_D$  pulse on pin 23 of the TDA933x. For optimum noise margin and reliable field detection, the edges of the  $V_D$  pulse should be positioned on <sup>1</sup>/<sub>4</sub> and <sup>3</sup>/<sub>4</sub> of the line period referring to the rising edge of the H<sub>D</sub> pulse as reference. (see Fig 4)

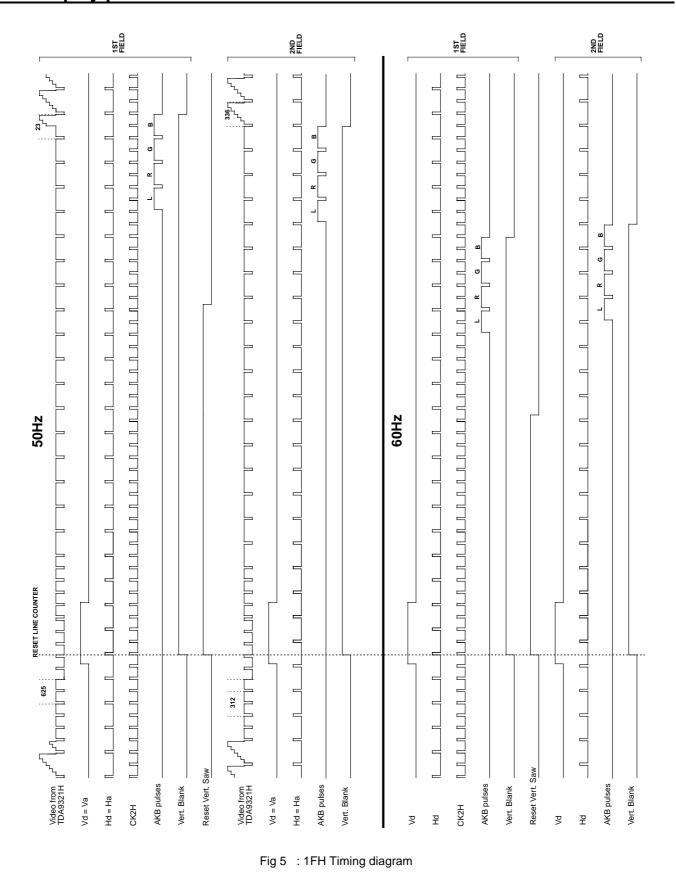

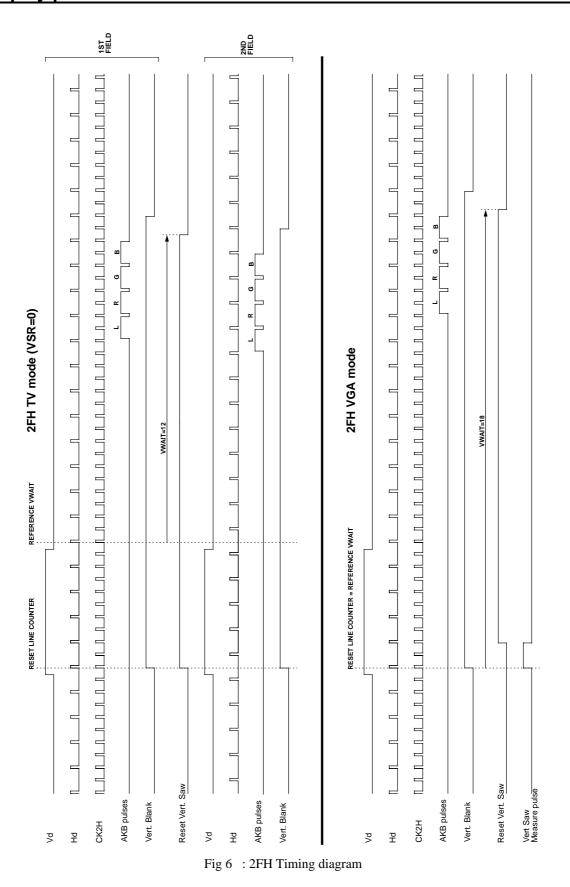

The timing of the vertical retrace for various modes will be discussed below and is also given in Fig 5 and Fig 6 at the end of this paragraph.

Internally, a clock signal is generated running at the double frequency of the horizontal output. This signal is indicated in the figures as "CK2H" (Cloc**K 2 H**-out) and is not related to the 2Fh frequency for double scan frequency.

#### TV mode

1 Fh mode:

When V<sub>D</sub> becomes high, the following actions are taken the first following clock pulse of the CK2H clock signal:

- The vertical line counter is reset

- Detection odd/even field by checking whether the CK2H clock pulse coincides with the horizontal blanking or not

- Vertical blanking starts and lasts 22 / 22.5 lines for 50 Hz and 17 / 17.5 lines for 60 Hz signals for odd / even fields

- A vertical saw reset is generated which discharges the vertical sawtooth capacitor to the reset level (2.3 Volt). The reset time is 14 lines for 50 Hz and 10 lines for 60 Hz.

#### See

Fig 5 and Fig 4.

#### 2 Fh mode

In this mode, two extra parameters can be set using VSR (Vertical Scan Reference) and VWT (Vertical WaiT). The bit VSR determines whether the rising edge or the falling edge of the  $V_D$  pulse is used as reference for the field detection and VWT.

The five bits register **VWT** sets the number of lines which the vertical sawtooth capacitor is kept to its reset level of 2.3 Volts and so determines at which line the vertical scan will start. The minimal number of lines is 8, putting a lower number in the **VWT** register will still generate 8 lines reset before the vertical scan is started. This function can be used to position the picture vertical correct for various modes of scan conversion boxes.

When V<sub>D</sub> becomes high, the following actions are taken the first following clock pulse of the CK2H clock signal:

- The vertical line counter is reset

- Vertical blanking starts. The duration is related to the VWT setting.

- The vertical saw reset is started.

- The actions below are executed on the timing, set by VSR:

VSR = 0: The first clock pulse of the CK2H clock signal, following the falling edge of the V<sub>D</sub> pulse

- VSR = 1: The first clock pulse of the CK2H clock signal, following the rising edge of the V<sub>D</sub> pulse

- Detection odd/even field by checking whether the CK2H clock pulse coincides with the horizontal blanking or not

- Start counting the number of lines set by VWT before releasing the vertical saw reset and starting the vertical scan. The total reset time is pending on the reference used for VWT:

For VSR = 0, the total reset time is the number of lines  $V_D$  lasts plus the number of lines, set by VWT.

For VSR = 1, the total reset time is equal to the number of lines, set by VWT.

See Fig 6 and Fig 4.

#### VGA mode

In this mode, always the rising edge of the  $V_D$  pulse is used as reference for field detection and **VWT** irrespective of the setting of **VSR**. It is possible to use **VWT** to determine the start of vertical scan.

When V<sub>D</sub> becomes high, the following actions are taken the first following clock pulse of the CK2H clock:

- The vertical line counter is reset

- Vertical blanking starts. The duration is related to the VWT setting.

- The vertical amplitude is stabilised

- Start counting the number of lines set by **VWT** before releasing the vertical saw reset and starting the vertical scan

- After 2 additional clock pulses of the CK2H clock (one line) the vertical saw reset is started. The total reset time is therefore VWT minus one line.

Also here, the minimal number of lines for **VWT** is 8. A lower number will still generate 8 lines reset before vertical scan is started.

Fig 4 : Field detection mechanism for VSR=0(A) and VSR=1(B)

#### **Philips Semiconductors**

# TDA9330/31/32 H TV Display processor

# Application Note AN98073

Philips Semiconductors

# TDA9330/31/32 H TV Display processor

# Application Note AN98073

#### Vertical frequency

#### TV mode

In TV mode, the vertical divider can be set to four different modes by the **SVF** (Set Vertical Frequency) and **VFF** (Vertical Free running Frequency) bit.. These modes determine the setting for 1 Fv or 2 Fv mode and the free running frequency in these modes when no valid  $V_D$  pulse is present

| SVF | VFF | 1Fh / 2Fh | Lines / field | Vertical frequency |

|-----|-----|-----------|---------------|--------------------|

| Х   | 0   | 1Fh       | 312.5         | 50 Hz              |

| Х   | 1   | 1Fh       | 262.5         | 60 Hz              |

| 0   | 0   | 2Fh       | 625           | 50 Hz              |

| 0   | 1   | 2Fh       | 525           | 60 Hz              |

| 1   | 0   | 2Fh       | 312.5         | 100 Hz             |

| 1   | 1   | 2Fh       | 262.5         | 120 Hz             |

#### VGA mode

In VGA mode, in free running mode the number of lines / field is fixed:

1 Fh VGA mode:288 lines(55.7 Hz when also no H<sub>D</sub> is present and Hout runs at 16.05 kHz)2 Fh VGA mode:576 lines(55.7 Hz when also no H<sub>D</sub> is present and Hout runs at 32.1 kHz)

The 1 Fh mode or 2 Fh mode is set by connecting pin 12 to ground (1 Fh) or leave pin 12 open (2 Fh).

#### **Catching ranges**

#### TV mode

| In TV-mode, | the catching range is:     |       |      |        |

|-------------|----------------------------|-------|------|--------|

| 1 Fh, 1 Fv: | 511.5 to 244 lines / field | (30.5 | to   | 64 Hz) |

| 2 Fh, 1 Fv: | 1023 to 488 lines / field  | (30.5 | to   | 64 Hz) |

| 2 Fh, 2 Fv: | 511.5 to 244 lines / field | (61   | to 1 | 28 Hz) |

#### VGA mode

For VGA, only the lines / field can be given. The vertical frequency is pending on the used horizontal frequency:

1 Fh VGA mode: 450 to 175 lines / field

2 Fh VGA mode: 900 to 350 lines / field

The vertical frequency range is determined by the automatic amplitude stabilisation circuit and ranges from 50 to 90 Hz.

#### Interlace

Interlace can be switched on and off by I<sup>2</sup>C bus **DL** (**D**e-interLace). To accommodate various TXT processors, also the choice can be made to delay the first or the second field with 0.5 line (reference is the  $V_D$  pulse) using bit **DIP** (**D**e-Interlace **P**hase).

#### \* Vertical sawtooth generator

The vertical sawtooth generator delivers the reference signals for vertical and horizontal geometry processor. An accurate reference current (Iref) of 100 $\mu$ A is realised by means of an internal bandgap reference voltage (3.9V) and an external resistor (39k $\Omega$ ). This 100 $\mu$ A reference current is used to derive a 16  $\mu$ A current to charge the external capacitor during vertical scan (1 Fh, 50 Hz). This circuitry ensures a very linear sawtooth (Usaw) that is used for further processing on vertical and horizontal (E-W).

| Philips Semiconductors |                  |

|------------------------|------------------|

| TDA9330/31/32 H        | Application Note |

| TV Display processor   | AN98073          |

#### \* TV-mode

The charge current for the sawtooth is automatically adapted pending on the input control bits **SVF** and **VFF** and the output control bit **FSI** (Field Synchronisation Information). **FSI** indicates whether the vertical frequency is 50/100 or 60/120 Hz and is only valid when a valid  $V_D$  pulse is present and **SL** (Sync Lock) = 1, indicating lock of the acquisition loop to a valid H<sub>D</sub> input. See the table below:

| SVF | VFF | FSI | 1Fh / 2Fh | SL | Charge current (µA) | Frequency (Hz) |

|-----|-----|-----|-----------|----|---------------------|----------------|

| Х   | 0   | Х   | 1Fh       | 0  | 16                  | 50             |

| Х   | 1   | Х   | 1Fh       | 0  | 19                  | 60             |

| 0   | 0   | Х   | 2Fh       | 0  | 16                  | 50             |

| 0   | 1   | Х   | 2Fh       | 0  | 19                  | 60             |

| 1   | 0   | Х   | 2Fh       | 0  | 32                  | 100            |

| 1   | 1   | Х   | 2Fh       | 0  | 38                  | 120            |

| Х   | Х   | 0   | 1Fh       | 1  | 16                  | 50             |

| Х   | Х   | 1   | 1Fh       | 1  | 19                  | 60             |

| 0   | Х   | 0   | 2Fh       | 1  | 16                  | 50             |

| 0   | Х   | 1   | 2Fh       | 1  | 19                  | 60             |

| 1   | Х   | 0   | 2Fh       | 1  | 32                  | 100            |

| 1   | Х   | 1   | 2Fh       | 1  | 38                  | 120            |

Furthermore the charge current can be adjusted with the I<sup>2</sup>C bus control, **VS** (vertical slope). The range is +/-20% should be used to compensate for tolerance of the external capacitor. When vertical zoom is applied, **VS** can be used to vary the position of the bottom part of the picture independent from the upper part (subtitle shift)

The external capacitor is discharged during vertical retrace by the vertical divider system, see above.

#### VGA mode

To prevent adjustment of the vertical amplitude for various VGA frequencies, the peak to peak amplitude of the vertical sawtooth at the sawtooth capacitor is measured and the charge current is adjusted to keep the amplitude constant independent of the vertical frequency.

The frequency range from this circuit is ranging from 50 to 90 Hz.

#### \* Vertical geometry processor

The sawtooth signal that is derived from the sawtooth generator can be controlled by I<sup>2</sup>C bus. Control functions are: VA (Vertical Amplitude), VSH (Vertical SHift), SC (S-Correction), VX (Vertical eXpand (zoom)), VSC(Vertical SCroll). To prevent picture damage, a built-in blanking functions blanks the RGB outputs for vertical overscan, larger than 105%. This function is active for both VX and VSC.

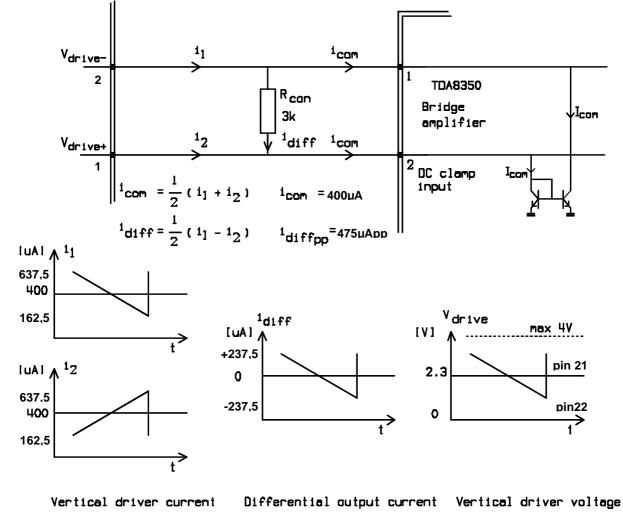

The vertical geometry processor has a differential current output for a DC coupled vertical output stage (drive). It is important to notice that the TDA933X is designed for use with a DC coupled output stage. This is the reason why a vertical linearity alignment is not necessary (and therefore not available).

A half picture blanking function (service blanking, **SBL**) is available for vertical alignment (See chapter alignment)

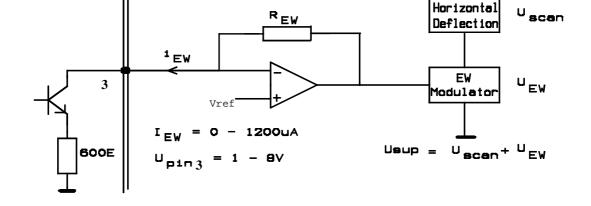

#### \* Horizontal geometry processor (E-W drive)

The horizontal geometry signal for E-W drive can control via the I<sup>2</sup>C bus the following functions:

EW (EW-Width), PW (Parabola/Width), CP (Corner/Parabola) and TC (Trapezium Correction).

The EW-width adjust range is such that linear zoom is possible on the picture size when used together with vertical expand (zoom).

The horizontal geometry processor has a single-ended current output for E-W drive.

#### Corrections for different scan frequencies and zoom

#### TV mode

Once all vertical and horizontal parameters are aligned, the geometry settings do not have to be adapted when changing to other vertical or horizontal scan frequencies.

Also when using zoom (horizontal and/or vertical) and vertical scroll (**EW**, **VX**, **VSC**) the geometry will remain correct without adapting the other geometry registers.

Note: this geometry adaptation only works when the correct geometry alignment procedure (see chapter "Geometry alignment") has been followed.

#### VGA mode

Also in VGA mode the geometry settings will remain correct for different horizontal and vertical frequencies. The horizontal geometry currents are proportionally adapted to the horizontal VCO frequency for this purpose.

#### \* EHT tracking + overvoltage protection

Both the vertical and the E-W drive can be modulated for EHT compensation.

This tracking makes the picture size independent of EHT variations due to the beam current. The compensation range is -5 to +5 % and is fixed for the vertical deflection. Therefore the circuit should be designed for correct tracking of the vertical amplitude. The horizontal compensation can be matched to the vertical compensation by setting **HCS**. The horizontal compensation range can be set from 0 to +/-7%.

A second function of this pin is for overvoltage protection, **XPR** (**X**-ray **PR**otection). **XPR** is set to "one" when the voltage on the pin exceeds 3.9 Volts and can be read by I<sup>2</sup>C bus. The bit is internally latched and will only be cleared when **XPR** is read after the voltage at pin 4 has dropped below 3.9 Volts. This ensures that the µprocessor can monitor a short exceeding of the 3.9 Volt level.

It is possible to switch the horizontal output automatically off via slow stop for **XPR** = 1 when **PRD** (PRotection Detection mode) is set to 1. When **XPR** becomes 1, the vertical scan is completed and after the vertical retrace the H-out is switched off via the slow stop procedure and the IC is set in stand-by mode. The  $\mu$ processor can check **XPR** and decide whether to start-up the set again or to generate an error message (e.g. blinking led).

Philips Semiconductors TDA9330/31/32 H

**TV Display processor**

# Application Note AN98073

A 2: Block diagram: Geometry on vertical and E-W drive

31

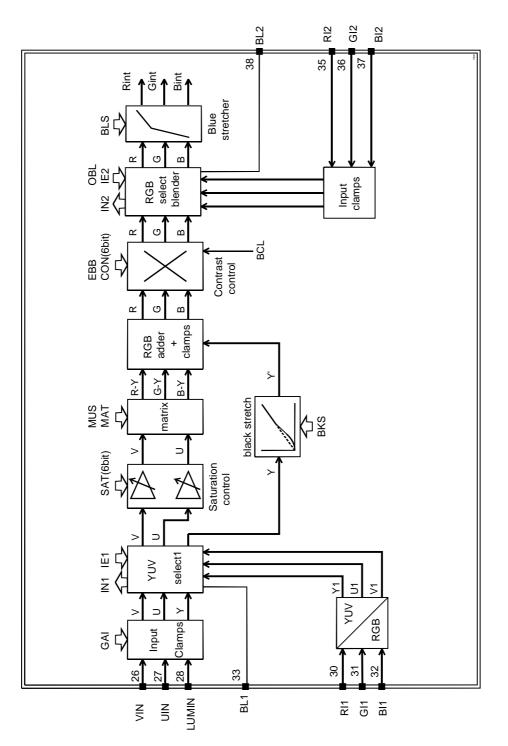

2.2.3 RGB processing and control

See also the related block diagram as well as the diagrams at the end of the report.

This paragraph can be divided into: -YUV/RGB selection -RGB-control

2.2.3.1 YUV/RGB selection

The main blocks are:

- YUV/RGB 1 insertion and selection

- Y, U and V signal processing.

- RGB-adder +clamps

- Contrast control

- Black stretcher

- Blue stretcher

- RGB2 signal selection

#### • Y, R-Y, B-Y/RGB 1 insertion and selection

The luminance and colour difference input signals should be AC coupled to the input pins. These input signals are internally clamped and supplied to the YUV selection circuit. By means of the I<sup>2</sup>C bus bit **GAI** an additional 10 dB amplification can be selected.

For RGB 1 insertion, the RGB signals should be AC coupled to the input pins where they are internally clamped. These RGB inputs are meant as external (SCART) inputs in 1Fh-mode and as VGA inputs in 2Fh mode..

The RGB1 insertion signals are converted to YUV signals by means of a RGB/YUV converter. The converter uses the inverse PAL matrix, so for correct colour reproduction the PAL matrix must be selected in the Y, B-Y and R-Y processing block (see also related paragraph). The YUV signal after conversion is supplied to the YUV source selector.

The YUV Source selector is controlled by hardware by means of the RGB1 insertion input signal BL1, (by applying an external voltage at this pin) and is designed for fast switching. The switching using BL1 can be enabled via the I<sup>2</sup>C bus by bit Insertion Enabled 1 (IE1). By means of the IN1 bit the RGB1 insertion pin status can be sensed. The status is only sensed during vertical retrace, so OSD insertion of descramblers will not set the IN1 bit.

The RGB 1 insertion inputs are linear (video) inputs.

| Philips Semiconductors |                  |

|------------------------|------------------|

| TDA9330/31/32 H        | Application Note |

| TV Display processor   | AN98073          |

#### \*Y, B-Y and R-Y signal processing/matrixing

The luminance signal is supplied to a black stretcher circuit. This circuit, which is only operational during line scan, extends the grey signal level towards the actual black level (i.e. actual black level is measured during burstkey). The amount of extension is dependent upon the difference between actual black level and the darkest part of the incoming video signal; it is thus dependent upon the IRE value of the video signal.

The darkest part of the video signal is registered on an internal-capacitor. For the black stretcher input/output characteristic, see the device specification. The black stretcher can be switched on/off via the  $I^2C$  bus (**BKS**). The black stretcher is fully integrated so the black stretcher time constant is fixed.

The saturation of the R-Y and B-Y signals is controlled via the I<sup>2</sup>C bus (SAT) The control range is minimal 52dB with a 6dB (minimum) reserve above nominal saturation level, refer also to the device specification.

The colour matrix can be controlled via the I<sup>2</sup>C bus bits (MAT) and (MUS). With the MAT -bit the PAL/SECAM matrix or NTSC matrix can be selected. With the MUS -bit selection of the Japanese NTSC matrix or USA NTSC matrix can be made.

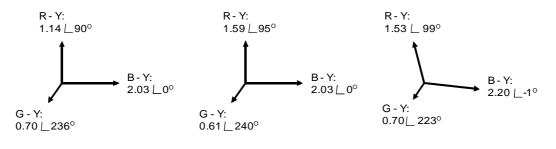

In Fig 7 the three matrices are given (see device specification).

Fig 7 : Matrix options

After the R-Y and B-Y processing the signals are added with the luminance signal in order to generate the internal RGB signals. At the same time a clamping action on the internal RGB-signals takes place.

**Note:** When using the RGB1 input, the PAL matrix must be selected to get correct colour reproduction. The matrix, used to convert the RGB signals at RGB1 to YUV for internal processing is inverse to the PAL matrix.

#### \*Contrast control

Contrast can be controlled for

- The internal video signal coming from the YUV-outputs of the TDA9321 (HIP) or from the YUV outputs of a scan conversion box (100Hz converter, progressive scan converter) or PAL plus decoder.

- RGB signals inserted via the RGB1 insertion inputs.

Contrast control has no influence on the second RGB insertion inputs which will be discussed later on in this chapter. More about contrast will be given in the paragraph "RGB-controls", in this paragraph an overview of all the controls are given The blue back, which can be activated by the  $I^2C$  bit **EBB**, is inserted at the contrast control function. When **EBB** is set to 1, a blue screen is inserted. This function can be used for example when no valid input signal is available, which usually is indicated by the coincidence detector of the input processor part.

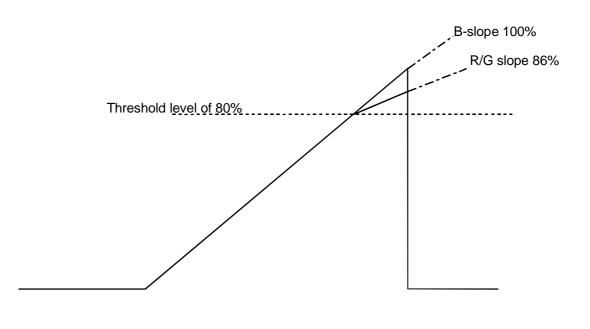

#### \* Blue stretcher

The standard blue stretcher of the TDA993X can be activated by the  $I^2C$  bit **BLS**. The blue stretcher reduces the R- and G-signals by 14% whenever the video signal exceeds a threshold level of 80%.

TV Display processor

### Application Note AN98073

Fig 8 : blue stretcher

When adjusting the white point be sure that the blue stretcher is inactive. In principal all features should be switched off during white point adjustments.

\*The second RGB input

This second RGB inputs are specially meant to insert teletext (TXT) or OSD signals.

Before the RGB signal selection the RGB signals are clamped to a similar DC level during burstkey period. Selection is controlled by the RGB insertion input switch. Fast insertion on the second RGB inputs is made active/inactive via the I<sup>2</sup>C bus (**IE2**). With the I<sup>2</sup>C bit **IN2** the status of the insertion switch input can be sensed. Two operating modes can be selected for the fast blanking pin 38 via I<sup>2</sup>C bit **OBL**:

- Normal fast RGB insertion 2 ( $R2_{IN} G2_{IN} B2_{IN}$ ) (**OBL** = 0)

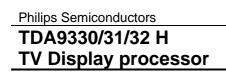

- A mixture of both signal sources (the blender function), i.e.  $R2_{IN}$ ,  $G2_{IN}$ ,  $B2_{IN}$  with YUV or RGB1 (**OBL** = 1). The normal fast insertion via the second RGB inputs is similar as described with the first RGB insertion inputs. If the blender function is selected then the voltage at the second RGB insertion input determines the amount of fading between the internal signal and the second RGB signals. In chapter "Application remarks per functional block and per pin" paragraph "RGB output and input circuit", pin 38 the blender characteristic is given (Fig 22).

The Blender input has been optimised on the blender output characteristic of the SAA5800 (µprocessor/OSD/teletext processor).

A 3: Block diagram: YUV/RGB processing.

Philips Semiconductors

### TDA9330/31/32 H TV Display processor

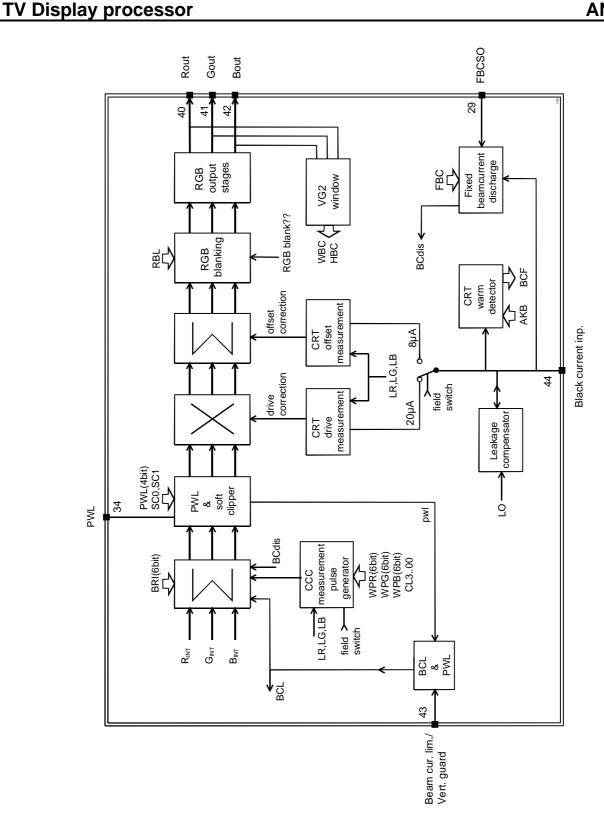

On page 43 the block diagram of the RGB-control is given.(see Fig A 4)

- \*RGB processing/ output stage

- \* Peak White Limiting / softclipper

- \*Beam current limiting

- \*RGB-outputs stages

- \*Continuous Cathode Calibration (CCC).

- \*Vg2 adjust window

- \*Fixed beam current discharge.

#### \* RGB processing

The selected RGB signals are via the I<sup>2</sup>C bus controlled on

- -contrast

- -brightness

-RGB white-point adjust (one individual control per channel)

Contrast can be adapted over a 20dB gain range (-14 dB to +6 dB) by means of the I<sup>2</sup>C function: **CONTRAST: 00 --> 63**. Nominal contrast setting (0 dB) is realised with I<sup>2</sup>C bus setting **CONTRAST = 44**.

For brightness, a change of DC-level of  $\pm 1$  V at RGB<sub>OUTPUT</sub> (w r t nominal) is possible for a change in I<sup>2</sup>C bus command (**BRIGHTNESS: 00 -> 63**). For nominal brightness (Brightness=32), the RGB<sub>OUTPUT</sub> is at black level which is equivalent to a I<sub>CATHODE</sub> of the CRT of 0mA. At the brightness function control signals used for the continuous cathode calibration circuit are inserted.

For white-point adjustment, a  $\pm 3$ dB change in channel gain is possible for a change in I<sup>2</sup>C bus commands (WHITE POINT ADJUSTMENT RGB (WPA R,G,B): 00 -> 63). Nominal white-point adjustment settings are realised with I<sup>2</sup>C bus settings WPA R,G,B = 32.

#### \*Peak white limiting /softclipper

The Peak White Limiting (PWL) of the TDA993X is controlled by is the  $I^2C$  control register **PWL**, which is a 4 bits register. This PWL function reacts on relative small white areas of the video signal. (for instance on inserted OSD-box). In front of the PWL function a low pass filter is added. The filter capacitor must be externally added, and allows adaptation of the filter characteristic. In order to have the same low pass filter characteristic of the peak white limiting for 1 Fh and a 2 Fh TV-sets the low pass filter is internally adapted to the selected 1 Fh or 2 Fh standard. This prevents that there is a difference between the PWL level 1Fh or 2Fh set.

Under the condition of maximum contrast and a video inputs signal with a small white box , (small such that the average beam current function is not active) the minimum and maximum PWL attack level can be defined as:

-Minimum PWL action (**PWL** setting 15)  $\rightarrow$  85% of the Y-input signal applied at the input(s) of the TDA933X -Maximum PWL action (**PWL** setting 00)  $\rightarrow$  55% of the Y-input signal applied at the input(s) of the TDA933X Besides a PWL function also a soft clipper is implemented. This soft clipper is only intended to clip high frequency peaks of the video signal. By I<sup>2</sup>C bits **SC1,0** the soft clipper level can be adjusted to four levels with respect to the with respect to the peak white limiter level, set by **PWL**. Take notice that there is a small PWL-level change due to the soft clipper action. The soft clipper will reduce high frequency peaks with about 15 dB.

#### \*Beam current limiting

The beam current limiting circuit or average beam current limiting (ABL) needs external circuitry to function. The voltage applied at the beam current pin must be a reflection of the amount of beam current through the picture tube. This function is a relative slow function and reduces the contrast and brightness of RGB signals.

For the average beam current limiting:

- contrast reduction begins when  $V_{BCL} < 3.0V$ ;

- brightness reduction begins when  $V_{BCL} < 2.0V$ .

$V_{BCL}$  is normally 3.3V when average beam current limiting (and peak white limiting) are not active. The contrast and/or brightness reduction of the RGB<sub>OUT</sub> is proportional to the voltage decrease on the BCL pin.

#### \* RGB output stages.

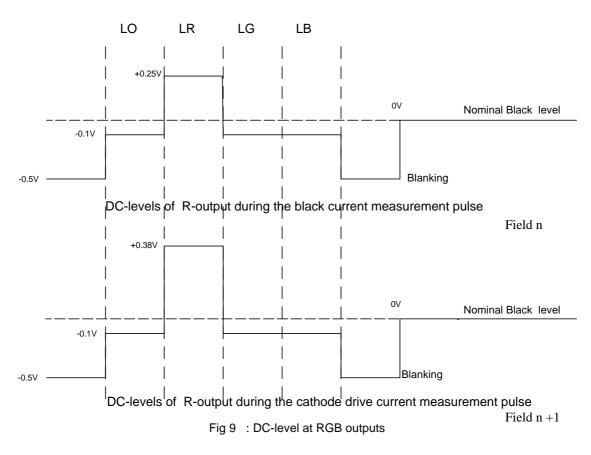

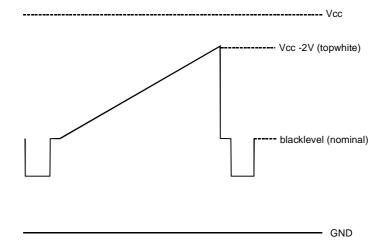

Before discussing the 2-point black current loop stabilisation or continuous cathode calibration loop (CCC-loop) it is perhaps better to discuss the RGB-output stages first. Because besides that at this function the H- and V-blanking are inserted, the DC-levels of the blanking are 0.5V below nominal black level of the video signal, also several DC-levels are inserted at the RGB-outputs. These levels are used as measuring lines for the CCC-loop. (see Fig 9). At the end of the vertical blanking ( line 18,19,20,21 for 1 Fh, 50 Hz) the measuring lines for (CCC)loop can be observed. The exact position of the measuring lines for various modes can be found in

Fig 5 and Fig 6 in chapter "Vertical synchronisation/deflection and geometry (horizontal & vertical)". These measuring pulses have three DC-levels:

-A DC-level of -0.1V with respect to nominal black level during the leakage measurement (LO). This level is chosen so that it lies close to the black level in order to have an accurate measurement close to cut off voltage of the picture tube.

-A pulse of +0,25V with respect to nominal black level, which corresponds with a cathode current of 8µA

-A pulse of +0,38V above nominal black level which corresponds with a cathode current of  $20\mu A$

The pulse-levels of +0.25V and +0.38V can only be seen measured on alternating fields. In the next paragraph CCC-loop will be described

Important to tell is that the RGB blanking level tracks with the DC level of the black current measurement pulses. The total video signal (except the measuring pulses for the CCC-loop) can be blanked by activating the I<sup>2</sup>C function **RBL** (RGB blanking). The RGB output stages supply the buffered RGB signals to pins 40, 41and 42 respectively.

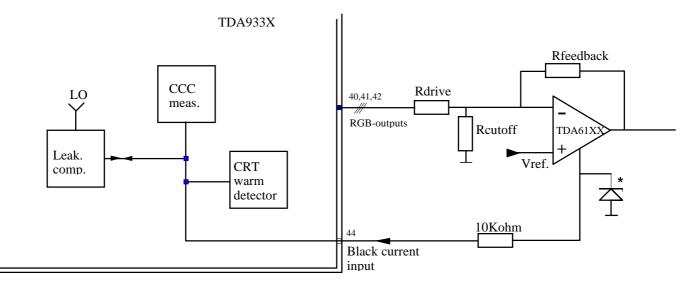

#### \* Continuous Cathode Calibration (CCC)

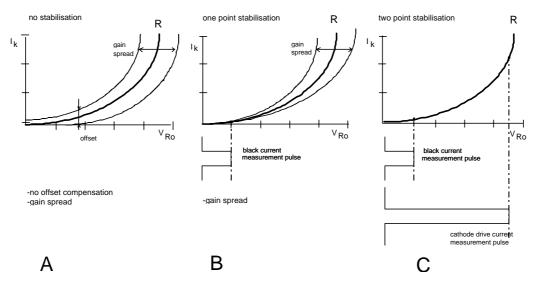

The Continuous Cathode Calibration (CCC) loop (or two point stabilisation loop) is an auto-tuning loop which stabilises the black level (offset) as well as the cathode drive level (gain) of each gun of the CRT sequentially and independently on alternating fields. The benefit of the CCC-loop can be best explained by the figure below.

Fig 10 : CCC-loop correction mechanisms

The graphs show the cathode current  $(I_K)$  as function of one of the three video output signals (in this case the red output) of the TDA933x.

In case of no stabilisation, the transfer characteristic changes as function of temperature and ageing of the tube. This results in an offset and gain error, see graph A. An one point stabilisation corrects for offset variations (graph B) however with the CCC-loop both offset and gain spread are compensated as given in graph C.

The CCC-loop can be divided into two loops:

-a black level stabilisation loop (cut -off compensation) -a cathode drive stabilisation loop. (gain compensation)

Besides these two loops a leakage current compensation loop is present.

This loop compensates the total offset current of the three cathodes of the picture tube and the offset of the three RGBamplifiers. The leakage current compensation range is about  $\pm 100\mu$ A. Leakage measurement and compensation occurs every field.

## TV Display processor

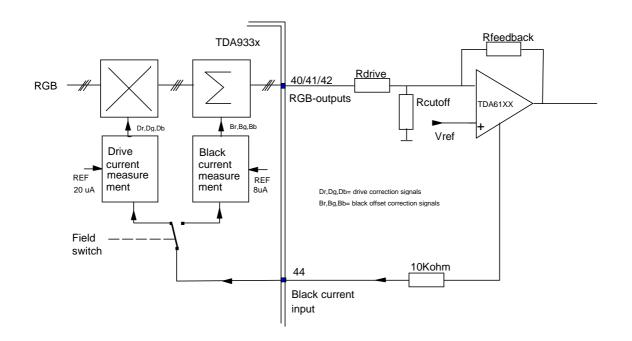

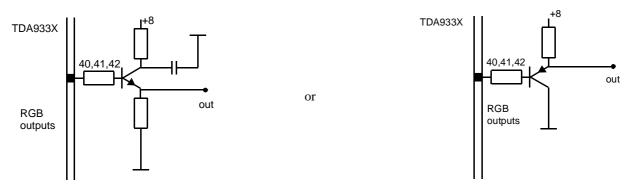

Fig 11 : Basic application of the CCC-loop with the TDA61XX

In Fig 11 basic application of the CCC-loop with RGB amplifiers is given.

In this figure the main two loops of black level stabilisation and cathode drive stabilisation are shown. The two loops are being stabilised on alternating fields by means of a field switch.

The main difference of the two loops is:

During black level stabilisation <u>internal black level clamps</u> ensure that <u>the DC-levels at RGB-outputs</u> are independently and sequentially changed so that always 8µA flows to the black current input (pin 44). during the 3 measurement lines (LR,LG,LB) for the black current offset levels. The black current offset correction signals are stored internally. During the cathode drive current stabilisation, <u>internal multipliers</u> ensure that <u>the cathode drive level for the three guns</u> of the CRT are independently and sequentially stabilised so that 20µA feedback current flows to the black current input (pin 44) during the 3 measurement lines (LR,LG,LB) for the drive levels. The correction for the drive signals are stored internally.

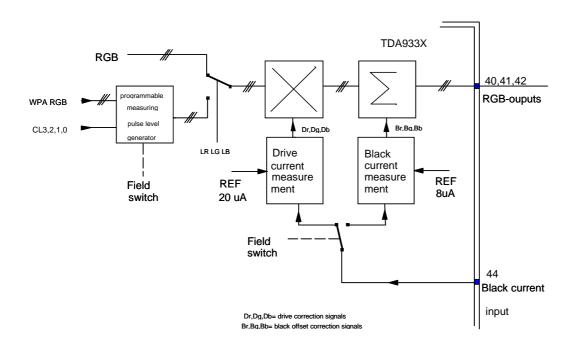

The drive levels at the three cathodes of the tube are always adjusted by the CCC-loop such that the feedback current is  $20\mu A$  This means that the gain of the RGB-amplifier, e.g. TDA61XX family, is NOT determining the drive level to the CRT anymore. In order to change the cathode levels at the picture tube four I<sup>2</sup>C bits are added **CL3..0**

Changing the cathode level at the picture tube is achieved in the following way:

The **CL3..0** bits vary the amplitude of the RGB channels together of the internal measurement lines generated in a programmable pulse generator. During the 3 measurement lines (LR,LG,LB) these levels are inserted on the RGB video signals.

Fig 12 : Main blocks of the CCC-loop

The drive correction signals (Dr, Dg, Db) will change the gain of the multipliers such that internal generated measurement pulse give a drive current measurement line at the cathode of the CRT corresponding with a current of  $20\mu$ A. This  $20\mu$ A current will be fed back to the black current input pin 44.

The drive correction signals(Dr,Dg,Db) will be stored internally so that, after the 3 measurement-lines(LR,LG,LB), the actual RGB-video signals will have the same multiplication factor as determined during the drive current measurement pulses.

The same procedure takes place during black current measurement except now the measurement lines are adapted such that a  $8\mu$ A cathode current is measured by adding the offset correction signals (Br, Bg, Bb) to the RGB-signals By means of the field switch the programmable measurement line level generator switches the internal measurement line level corresponding with a  $20\mu$ A cathode to a internal level corresponding with a  $8\mu$ A cathode current.

The field switch is not synchronised with odd / even fields.

Changing the WPA RGB registers works on the same way as changing the **CL3..0** bits except this three registers react on each individual RGB signal where the **CL3..0** bits react on all three RGB-signals together.

So when changing the WPA RGB registers the internal generated measurement lines are adapted at the input of the CCCmultiplier the CCC-loop adjust itself so that the black current measurement lines at the black current input (pin 44) are constant ( $8\mu$ A and  $20\mu$ A).

## TV Display processor

#### Start up behaviour of the CCC-loop.

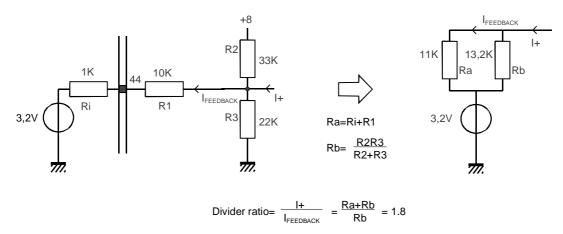

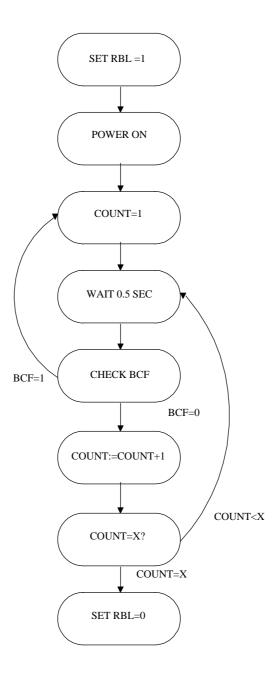

After H-out is released the RGB-outputs are blanked and the CCC-loop is direct active, so from the start the 250mV and 380mV measuring pulses are present at the RGB-outputs. The cathodes of the picture tube are driven by the 250mV and 380mV measuring lines but due to the fact that the tube is cold (heater voltage is just applied, emission is very low) the corresponding  $8\mu$ A and  $20\mu$ A are not measured at the black current input so the gain as well as the offset is set to maximum by the CCC-loop what results in the fact that the CCC-loop gets out of range. This means that the amplitude of the 3 measuring lines is maximum at the RGB outputs. (actual scan remains at blanking level). After 7 to 15 seconds, the heater has warmed up the cathodes to generate enough emission. At that moment the CCC-loop starts to measure  $8\mu$ A and  $20\mu$ A at the black current input pin and at the same time the I<sup>2</sup>C Black current loop failure sense bit **BCF** becomes zero, at which moment the RGB-outputs will be released.

For applications without a picture tube the CCC-loop can be switched off by means of the I<sup>2</sup>C control bit **AKB** (Auto Kine **B**iasing). In case **AKB** is switched off the RGB blanking and **WPA R,G,B** registers are disabled.

In principal there is no difference in working for the CCC-loop in 1 Fh or 2 Fh mode. In both modes, the three measuring lines R, G and B are generated, each lasting one line period. (See Fig 9, page 37) Each alternate field the cut-off level (8  $\mu$ A) or the drive level (20  $\mu$ A) is measured and adjusted. The only difference is the timing of the internal measurement window of loop.

For 1 Fh applications the measurement window starts at 50% of the measuring line and stops at 75% of the line. The measurement windows duration is  $16\mu$ s

For 2 Fh applications the measurement window starts 25% of the measuring line and stops at 75% of the line So the measurement window duration is also 16µs. Since the measuring window duration in 1 Fh and 2 Fh is equal all internal time constants of the CCC-loop are not dependent on 1 Fh or 2 Fh mode.

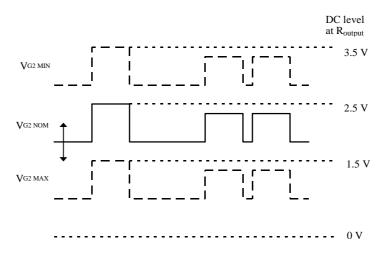

#### \*VG2 window

Via the I<sup>2</sup>C bus VG2 can be aligned in production. The TDA933X measures automatically the DC-level of the measuring lines of the cut-off loop of the CCC-loop.

Internal, a window is defined of 2.5 Volt  $\pm$  100 mV. By turning the VG2 potentiometer the DC-level at the RGB-output will change. Whenever the lowest DC-level of the three RGB-outputs is within this window the VG2 is correctly aligned. Note that the lowest RGB output corresponds with the highest cut-off level at the cathode of the picture tube. "Within window" can be read back with the I<sup>2</sup>C output bit **WBC**. With the **HBC**-bit can be monitored whether the DC-level is above or below this window.

The only restriction on this alignment method is that the VG2 window is fixed at a DC-level of  $2.5V \pm 100$ mV. This implies that the RGB amplifiers should be designed to have the required highest (raster) cut-off level at their outputs at 2.5 Volt DC input level. The raster cut-off level is 10 - 12 Volt lower than the usual specified spot cut-off level.

#### \*Fixed beam current discharge

This function " fixed beam current switch off" is used to discharge EHT voltage of picture tubes without bleeder when switching to standby or switching off the power supply. By means of the IIC function "Fixed Beam Current switch off" **FBC**=1 this function can be enabled. In combination with the IIC function Switch Off in vertical Overscan (bit **OSO**) can be determined whether the set is discharged in vertical overscan or during normal scan. There is in difference in behaviour of this function between switching to standby and switching off the power supply using the mains switch. So has pin 29 no function when the set is switched to standby (**STB1,0**).

Therefore the function will be explained below for both switching off the power supply using the mains switch and for switching to stand-by using **STB1,0**.

Switching the power supply off using the mains switch:

The power supply (the deflection supply) is "sensed" with an external circuit. The status of the power supply is fed to pin 29. A voltage below the 1.5V at this pin 29 means the supply works normally. When the supply voltage drops, pin 29 should be pulled above 1.5 Volt. This activates the fixed beam current function (provided bit **FBC**=1) and the following procedure is started:

- The vertical scan is completed and vertical flyback is made

- Inside pin 44 "the black current input" a current measurement of 1mA is activated. This current is adjusted and kept at 1 mA by adapting the brightness level of the RGB outputs. In other words: the brightness control discharges the tube, the discharge current of 1mA is measured via the black current input pin 44.

- The discharge takes place during the overscan when OSO bit =1 which minimises the visability of the discharge on the screen of the picture tube.

- The discharge begins when the voltage at pin 29 becomes high and ends when the supply voltage of the TDA933X drops below the power on reset level (about 6.2V). When a power on reset is detected both H-out and the discharge current are disabled.

#### Switching to stand-by using **STB1,0**:

When switching the IC to Standby mode also discharge of the EHT voltage can take place when FBC=1.

The procedure is the same as above (including the use of **OSO**) except:

- Pin 29 has no function

- A slow stop is made by the horizontal output. This means that the T-on of H-out decreases linear from nominal to zero in 43msec During the first 38ms of the slow stop time the fixed beam current switch off is activated in order to discharge the EHT voltage.

See also chapter "Horizontal synchronisation", paragraph "H-output and slow start/stop"

## Application Note AN98073

A 4: Block diagram: RGB-processing and control.

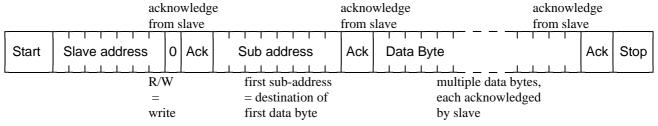

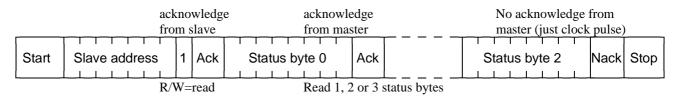

#### 2.2.4 I<sup>2</sup>C bus description

#### 2.2.4.1 Overview I<sup>2</sup>C bits

#### For easy control, most functions of the TDA933X are controlled via the $I^2C$ bus:

| <b>Input</b> functions <sup>1)</sup> |            | Sub   | Data bits |     |      |      |     |     |                   |     |

|--------------------------------------|------------|-------|-----------|-----|------|------|-----|-----|-------------------|-----|

| (write)                              |            | addr. |           |     |      |      |     |     |                   |     |

|                                      |            | (hex) |           |     |      |      |     |     |                   |     |

|                                      |            |       | D7        | D6  | D5   | D4   | D3  | D2  | D1                | D0  |

| RGB processing-1                     |            | 00    | MAT       | EBB | SBL  | RBL  | BLS | BKS | IE1               | IE2 |

| RGB processing-2                     |            | 01    | MUS       | FBC | OBL  | AKB  | CL3 | CL2 | CL1               | CL0 |

| Wide horizontal blanking             |            | 02    | HBL       | 0   | GAI  | STB0 | HB3 | HB2 | HB1               | HB0 |

| Horizontal deflection                |            | 03    | 0         | VSR | FAST | STB1 | POC | PRD | VGA <sup>2)</sup> | ESS |

| Vertical deflection                  |            | 04    | 0         | VFF | LBM  | DIP  | OSO | SVF | EVG               | DL  |

| Brightness                           | BRI        | 05    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Saturation S                         | SAT        | 06    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Contrast C                           | CON        | 07    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| White point Red V                    | <b>WPR</b> | 08    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| White point Green V                  | WPG        | 09    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| White point Blue W                   | <b>WPB</b> | 0A    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Peak White Limiting P                | WL         | 0B    | 0         | 0   | SC1  | SC0  | A3  | A2  | A1                | A0  |

| Horizontal Shift H                   | ISH        | 0C    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Horizontal Parallelogram             | HP         | 0D    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| E-W amplitude                        | EW         | 0E    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| E-W parabola/width                   | PW         | 0F    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| E-W corner parabola                  | CP         | 10    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| E-W trapezium                        | TC         | 11    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| E-W EHT hor.comp.sens.               | HCS        | 12    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Vertical slope                       | VS         | 13    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Vertical amplitude                   | VA         | 14    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| S-correction                         | SC         | 15    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Vertical shift                       | VSH        | 16    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Vertical Zoom                        | VX         | 17    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Vertical Scroll                      | VSC        | 18    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

|                                      | WT         | 19    | 0         | 0   | 0    | A4   | A3  | A2  | A1                | A0  |

| DAC output <sup>3)</sup> D           | DAC        | 1A    | 0         | 0   | A5   | A4   | A3  | A2  | A1                | A0  |

| Output (read)                        |            |       | Data bits |     |      |      |     |     |                   |     |

| Status byte 0                        |            | 00    | POR       | FSI | SL   | XPR  | NDF | IN1 | IN2               | WBC |

| Status byte 1                        |            | 01    | ID3       | ID2 | ID1  | ID0  | NHF | BCF | FLS               | NRF |